Much of what happens at LBNL is "taking pictures"

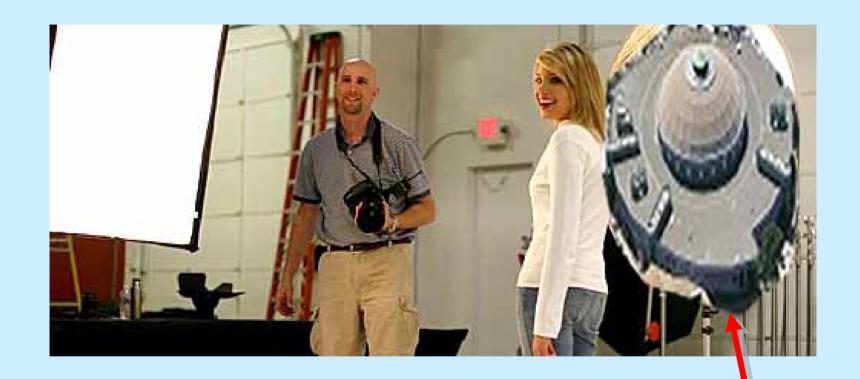

We worry a lot about getting just the right lighting ...

And of course about the subject ...

But less often "the camera" ...

# One Picture is Worth ... Solid State Imaging Detectors

Many objects imaged with visible light

x-rays (ALS)

electrons (EM)

and other charged particles

# Desirable

- **♦** (x,y)

- q (or n)

- E (or λ)

- **†**

- $X: \infty \text{ (or } N = X/\delta: \infty)$

- ♦ Frame rate: ∞

- **♦** Dynamic range: ∞

- Non-linearity: 0

- Cost: 0

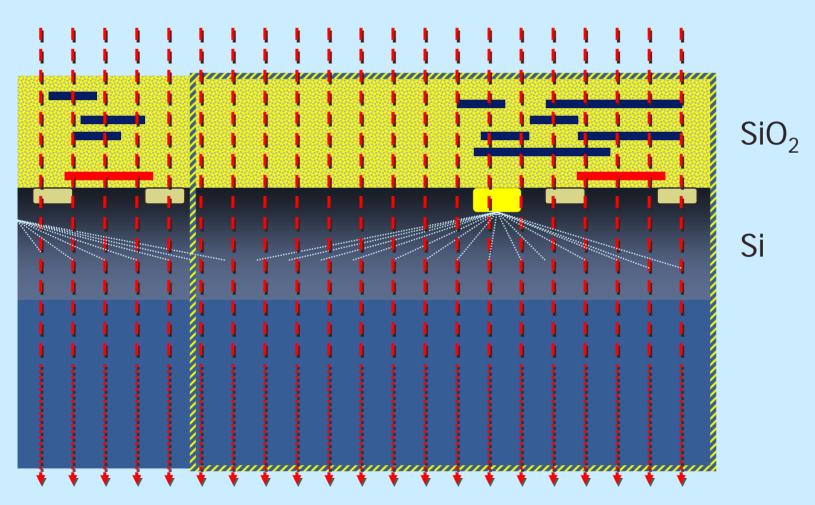

## **Solid State Imager**

N+ contact

p Si

Depletion region

Generally some sort of diode array (Title is general – talk is about Si)

Continuity equation

$$\frac{\partial n}{\partial t} = \mu_n n \nabla E + D_n \nabla^2 n + G_n - R_n$$

Drift:  $v=\mu E$

Diffusion:  $D = \frac{kT}{q}\mu$

# Also important

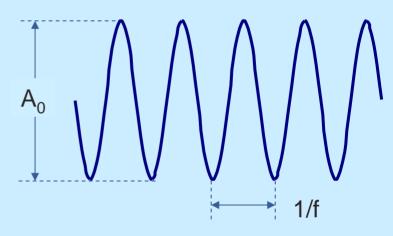

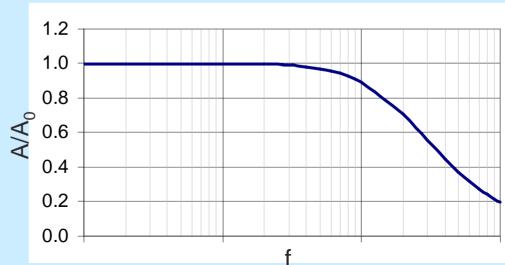

$\rightarrow$  MTF: fft(PSF)

Point spread function – determines spatial resolution

# Oh, this also helps

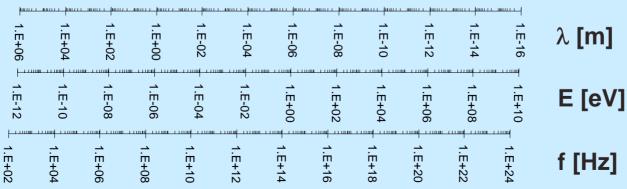

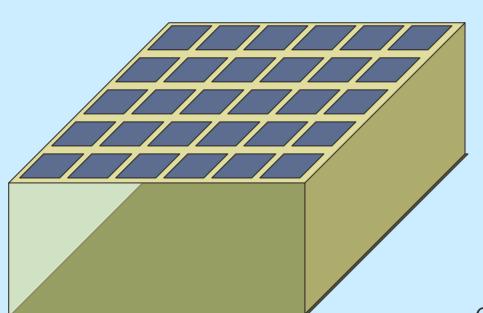

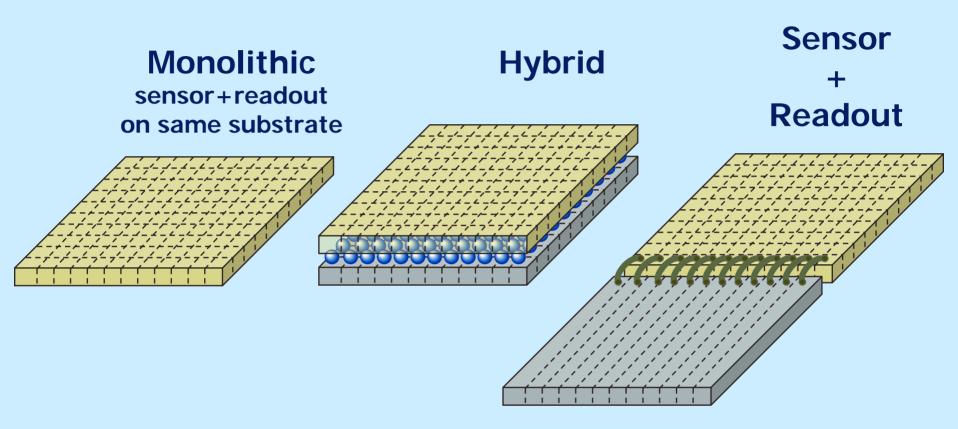

# Topology

2D segmented Si

2D segmented Si attached to 2D segmented Si

2D segmented Si attached to 1D segmented Si or other electronics

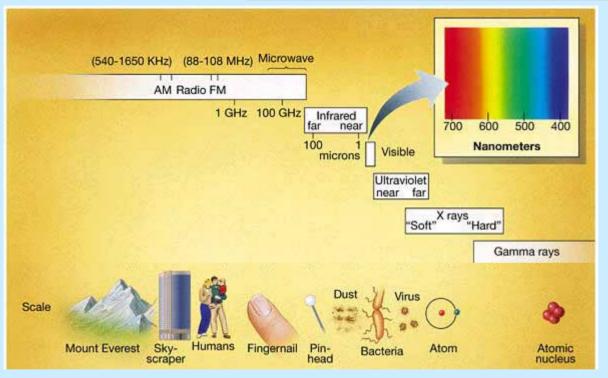

#### Start with small, but useful, part of spectrum

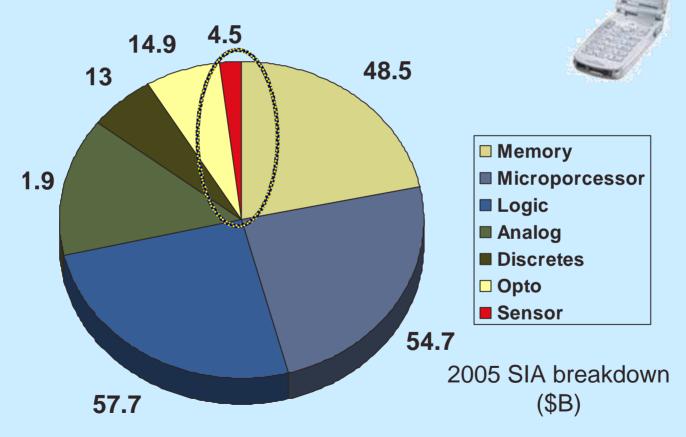

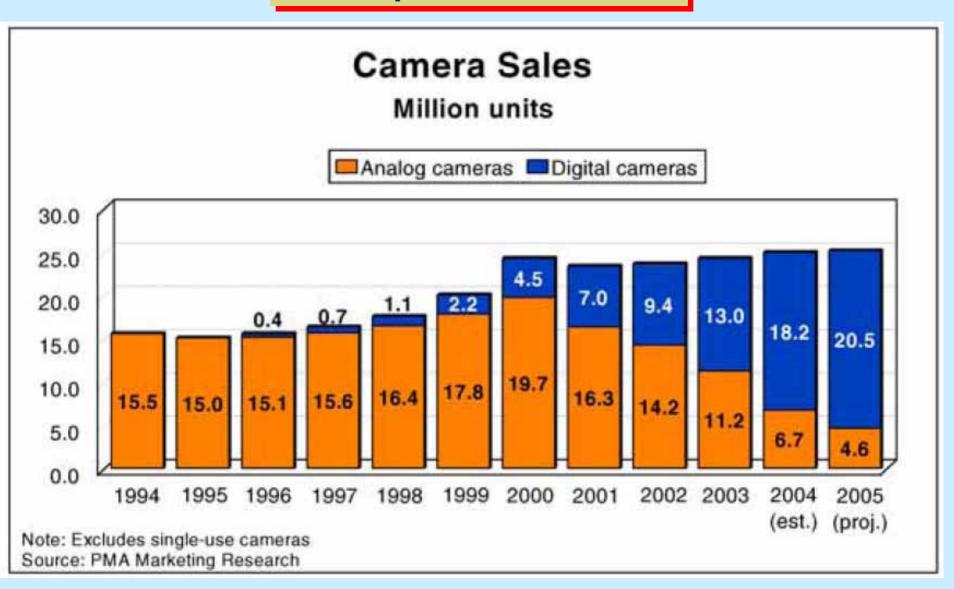

Consumer imaging is a many \$B/year industry (driven, of course, by such critical needs as →

What can we learn? What can we do better?

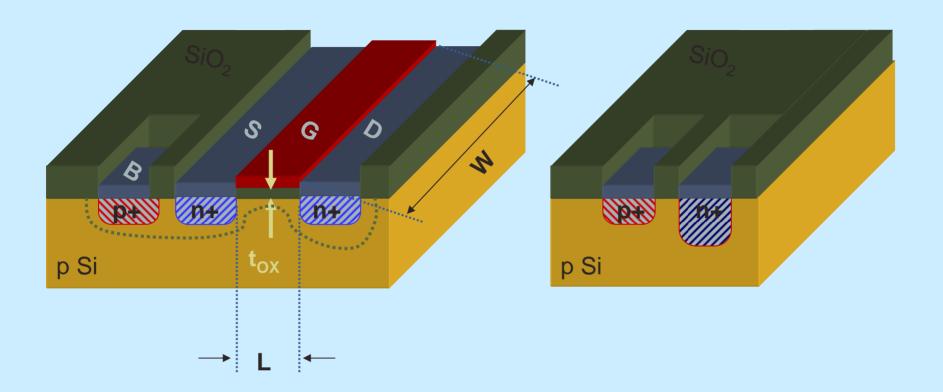

# **Integrated Circuit Elements**

**MOS Transistor**

pn Diode

#### **Conventional Semiconductor Processing**

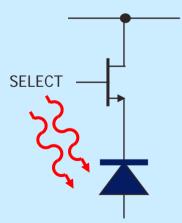

- Passive Pixel Sensor

- Proposed 1968

- No in-pixel reset

- Poor performance due to capacitive load (nothing buffers the photodiode)

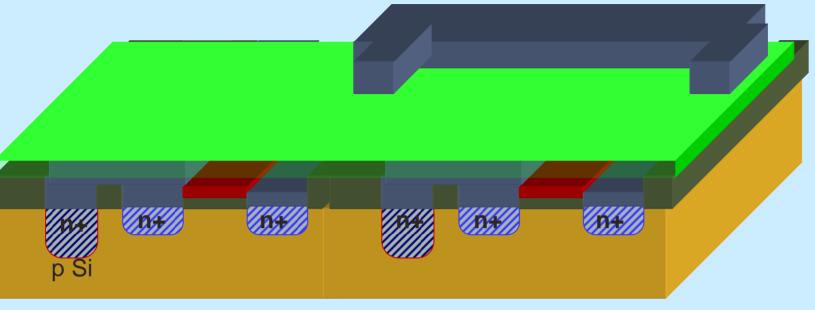

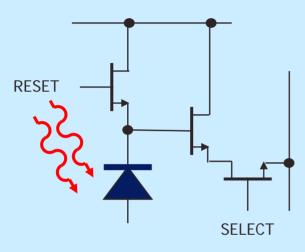

### **Active Pixel Sensor**

- Active Pixel Sensor

- Also proposed 1968

- Many ways to make the photodiode

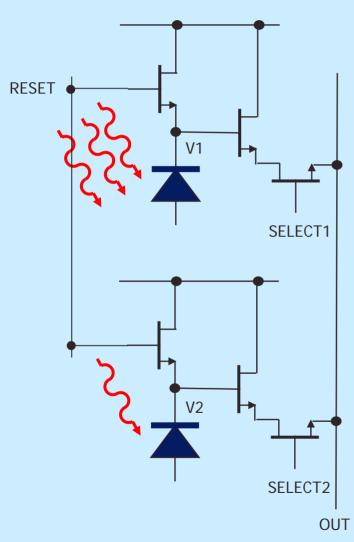

# **How It Works**

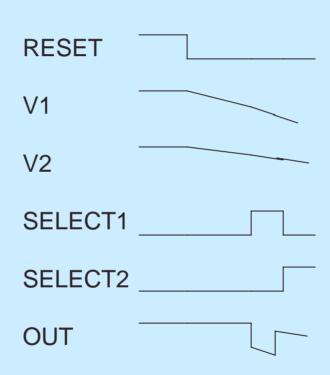

# **Add Microlens and Color Filter**

- Microlens array recovers some of the fill factor

- Opaque walls between cells reduces cross-talk

- Color pattern matched to algorithm

# **Integrated Circuit Elements**

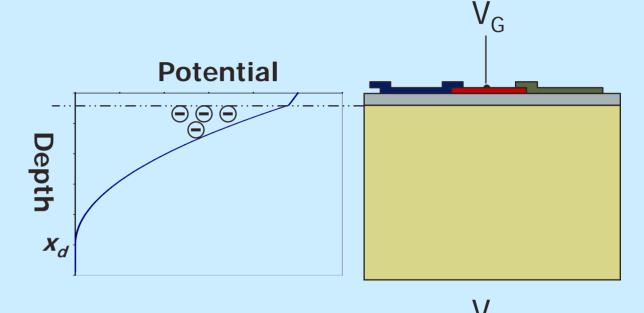

$$C = \frac{1}{\frac{1}{C_{OX}} + \frac{1}{C_{DEP}}}, \quad C_{OX} = \frac{\varepsilon_{SiO_2}}{t_{OX}}, C_{DEP} = \frac{\varepsilon_{Si}}{x_D}$$

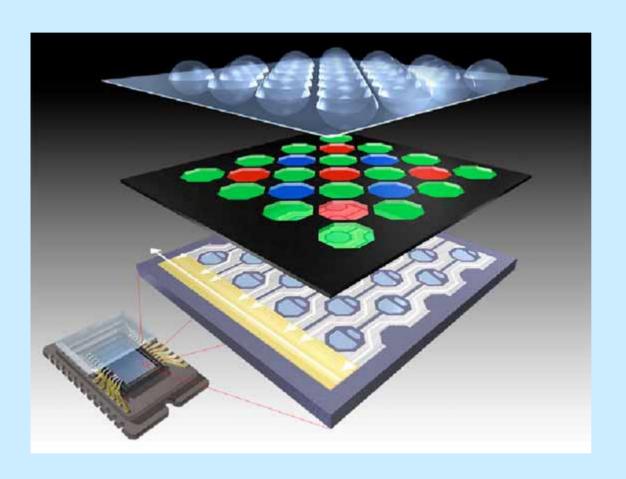

# **MOS Capacitor**

# **Accumulate Charge**

# **Accumulate and Transfer Charge**

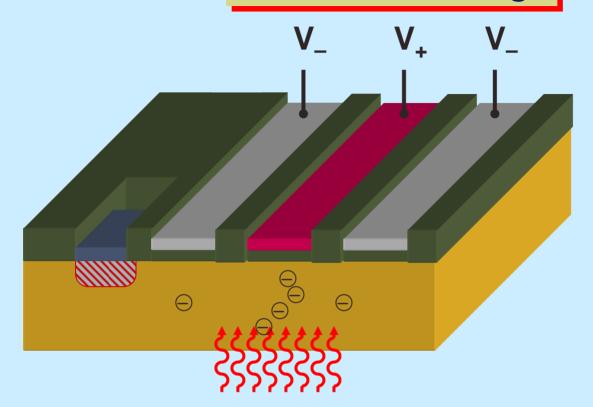

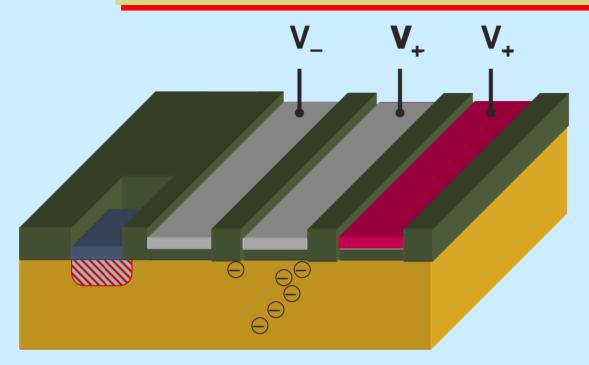

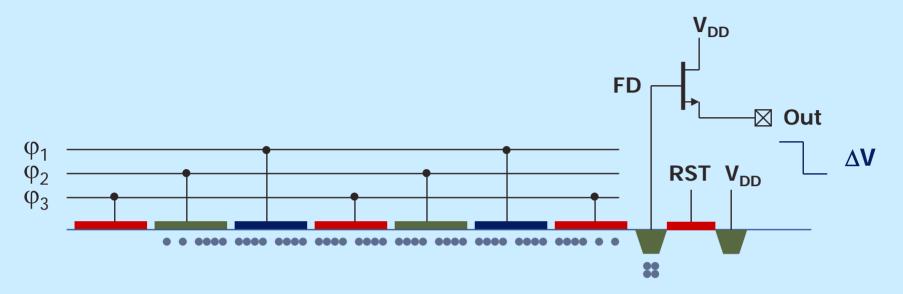

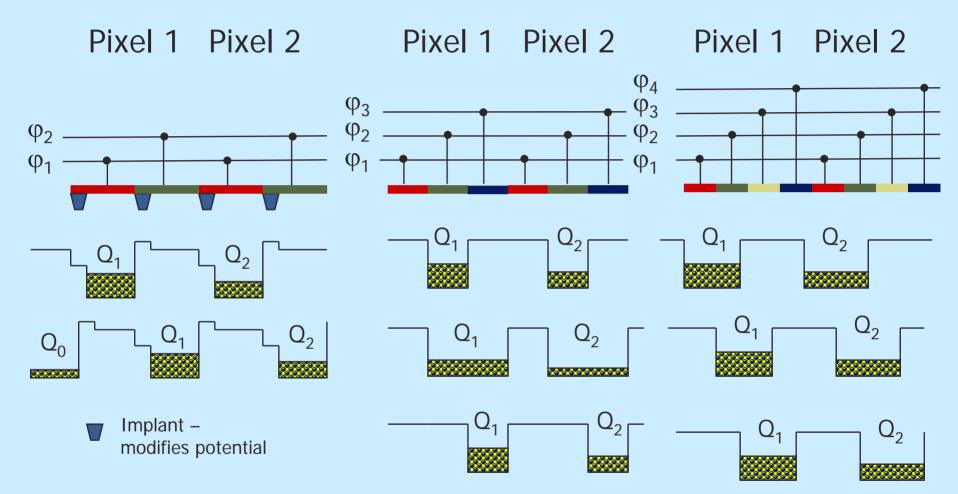

#### **Conventional 3-Phase CCD**

- Noiseless, ~lossless charge transfer

- High gain charge-to-voltage conversion  $\Delta V = q/C_{FD}$

- Output amplifier (source follower, or ...) on-chip

### **Scientific CCDs**

Dumbbell nebula - LBNL CCD

Blue: H- $\alpha$  at 656 nm Green: SIII at 955 nm

P. Denes July '06 I3

Red: 1.02 mm

- CCD invented in 1969 by Boyle and Smith (Bell Labs) as alternative to magnetic bubble memory storage

- LST ("Large Space Telescope" later Hubble) 1965 – how to image?

- Film was obvious choice, but It would "cloud" due to radiation

damage in space

Changing the film in the camera

not so trivial

- 1972 CCD proposed

# Many ways to do this

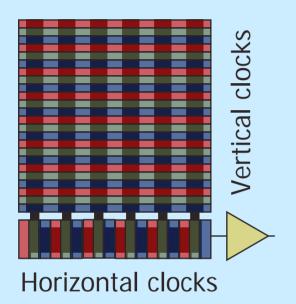

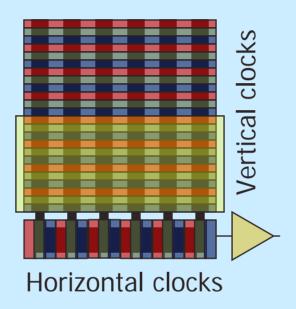

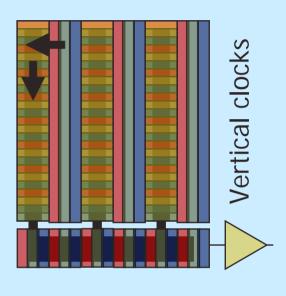

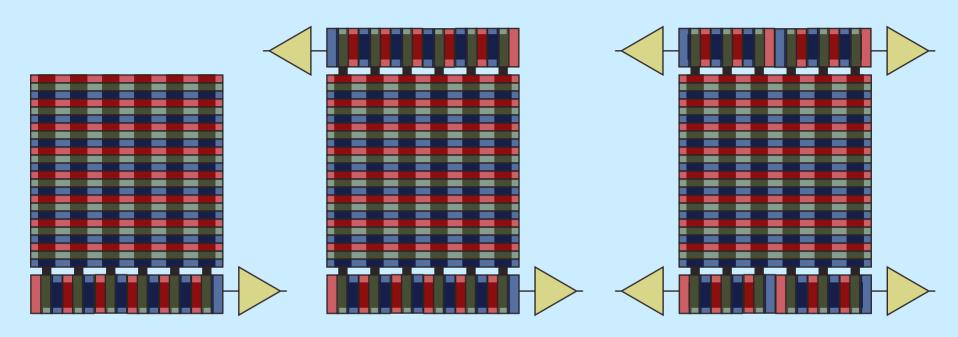

#### **Several architectures**

Horizontal clocks

Full frame

Frame transfer

Rapid shift from image

to storage

Slower readout of

storage during integration

**Interline**

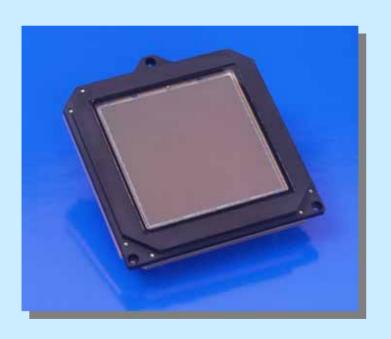

# Very Large Format CCDs (and CMOS imagers)

- Fairchild Wafer Scale Full Frame CCD

- 9216 x 9216 x 8.75 µm pixel

- 80.64 x 80.64 mm<sup>2</sup> size CCD

- Eight 3-stage output amplifiers

- Readout noise < 30e- @ 2/fps</li>

- Cypress CYIHDS9000

- 3710 x 2434 x 6.4 µm pixel

- 23.3 x 15.5 mm<sup>2</sup> size APS

- 0.13 µm imaging CMOS process

- Canon 16.7 MPix

- 36 x 24 mm<sup>2</sup> 4992 x 3328

- Kodak 39 MPix

- 36 x 48 mm<sup>2</sup>

### **APS vs CCD**

- APS moves a voltage down the column

- CDS either in pixel or "digital"

- Addressable readout

- Backside illuminated devices not yet really practical

- Support circuitry (clock drivers, digitizers) required

- CCD moves a *charge* down the column

- "Intrinsic" CDS

- Sequential readout

- Backside illuminated devices practical (thick ones, too)

- Can be monolithic one chip

Otherwise roughly the same. In principle, equivalent dynamic range. In principle, same leakage current (but not in practice)

Monolithic device much more profitable → prevalence in market

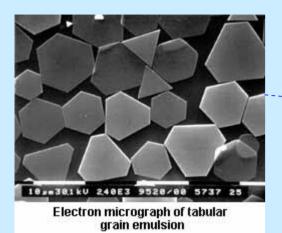

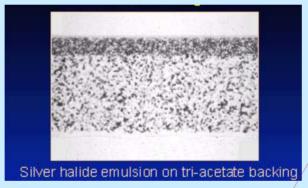

# The Competition - Film

AgX + gelatin (emulsion)

backing

sub-micron to few micron grains CMOS / CCD  $\sim$ 7 – 10  $\mu$ m

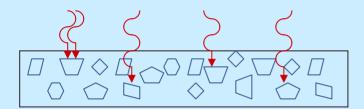

#### **How it works**

#### Incident light

phototelectrons convert Ag<sup>+</sup> sites to Ag<sup>0</sup> – at the same time, thermal fluctuations tend to "erase" the image. Generally, a few photons are required to leave a "latent" image on a grain

larger grains have larger cross section, so they are more likely to get hit. Thus, larger grains are "faster" but "grainier"

#### **How it works**

"develop" the image so that the sensitized AgX is reduced to black metallic silver "fix" the image – removing the unexposed AgX

The chemistry and physics of photographic film is not trivial

#### **Historical Footnote**

George Eastman

"You press the button, we do the rest"

Hannibal Goodman

Minister at the House of Prayer in

Newark, New Jersey

(files for patent in 1887 – granted 1898)

The devil is in the details: "photographic plates" (emulsion on glass) → cellulose nitrate for first motion pictures (tends to burn – don't yell "fire" in a theater → "safety film" (Kodak 1911) – not really perfected until 1948 (triacetate)

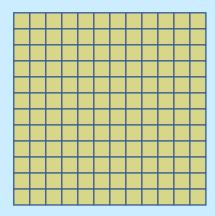

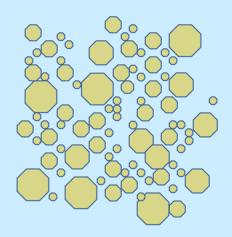

# Who Wins?

#### Silicon

Regular array of pixels pitch p

Random collection of different grain sizes

#### Film

#### For now film grains smaller than silicon pixels

Analog

**Digital**

# **Pros and Cons**

Silicon

Film

| <b>♦</b> | Processing          | Electronic                                                                                 | Chemical                                                                             |

|----------|---------------------|--------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|

| •        | Linearity           | "ideal" $n(e^-) = QE \times n(\gamma)$                                                     | non-linear – n $\gamma$ required to flip a grain; thermal fluctuations vs grain size |

| <b>♦</b> | Resolution          | Larger pixels                                                                              | Smaller grains                                                                       |

| <b>♦</b> | Dynamic range       | CCDs – 16 bits                                                                             | Locally, ~4 bits                                                                     |

| •        | Integration<br>time | Ultra-high quality<br>process – minutes; opto<br>process – seconds;<br>normal process – ms | "long" (also thermally limited)                                                      |

| •        | MTF                 | Regular pattern – aliasing                                                                 | Given by smallest grains, no aliasing                                                |

| <b>♦</b> | MTF x S/N           | Better                                                                                     | Worse                                                                                |

#### Marketplace has decided

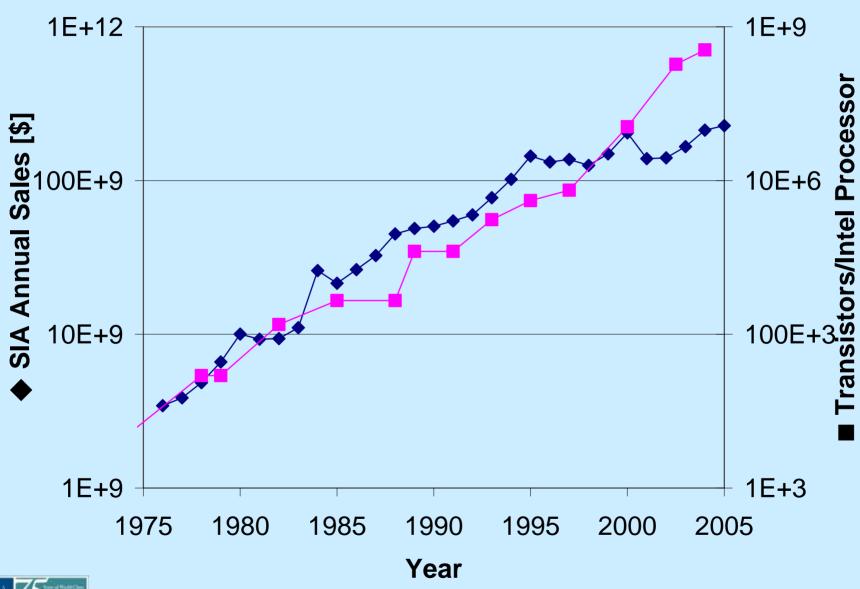

# **Technical Drive for Industry**

#### **Exponential Growth Achieved by Feature Size Shrinkage**

Size: WL

$$g_m \sim \mu \frac{\mathcal{E}_{SiO_2}}{t_{OX}} \frac{W}{L} (V_{DD} - V_t)$$

$$C \sim \frac{\mathcal{E}_{SiO_2}}{t_{OX}} WL$$

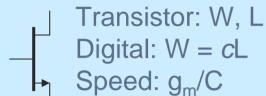

# CMOS driven by constant field scaling\*

Channel Length L  $\rightarrow$ L  $/\kappa$

# Why constant field scaling?

Area

$$g_m \sim \mu \frac{\mathcal{E}_{SiO_2}}{t_{OX}} \frac{W}{L} (V_{DD} - V_t)$$

$$C \sim \frac{\varepsilon_{SiO_2}}{t_{OX}} WL$$

Speed  $\sim g_m/C$

Power ~CV<sub>DD</sub><sup>2</sup>/speed

Power density ~Power/Area

Scale geom. W, L,  $t_{OX} \downarrow_{K}$

$1/\kappa^2$

ĸ

$1/\kappa$

$\kappa^2$

ĸ

$\kappa^3$

Scale voltages too  $V_{DD}$  and  $V_{T}$  also  $\downarrow \kappa$

$1/\kappa^2$

1

$1/\kappa$

K

$1/\kappa^2$

1

# **What This Means**

| Feature Size<br>[nm]      | 2000 | 1200 | 800  | 500  | 350  | 250  | 130  | 65   | 35   | 20   |

|---------------------------|------|------|------|------|------|------|------|------|------|------|

| Minimum<br>NMOS           |      | 4    | 4    | #    | 4    | *    | *    | ۵    | •    | 0    |

| V <sub>DD</sub> (V)       | 5.0  | 5.0  | 5.0  | 3.3  | 3.3  | 2.5  | 1.3  | 1.2  | 1.1  | 0.8  |

| t <sub>ox</sub> (Å)       | 350  | 250  | 180  | 120  | 100  | 70   | 30   | 13   | 9    | 6    |

| Oxide field<br>(106 V/cm) | 1.4  | 2.0  | 2.8  | 2.8  | 3.3  | 3.6  | 4.3  | 9.2  | 12   | 13   |

| Production                | 1980 | 1983 | 1988 | 1991 | 1995 | 1997 | 2001 | 2003 | 2007 | 2012 |

# Why not combine CMOS and CCD?

a dream process?

CCD pixel region

CMOS amplifiers/digitizers

CCDs have certain specialized requirements

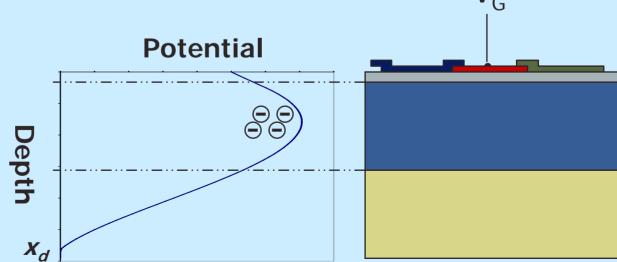

#### Surface vs buried channel CCD

- MOS capacitor

- Potential maximum at Si – SiO<sub>2</sub> interface

- CTE < 1 due to trapping at interface

- Potential maximum not at SiSiO<sub>2</sub> interface

- CTE typically > 99.9999%

### Why not combine CMOS and CCD?

a dream process?

CCD pixel region

CMOS amplifiers/digitizers

CCDs have certain specialized requirements

- buried channel

- triple poly (for 3-phase CCDs)

- deep implants, thick low doping regions, thick gate oxides (high voltages) all go in the opposite direction of shrinking CMOS

#### **CCD vs APS**

- CCD will survive (genuinely better for certain applications see below), and will continue to be the best solutions for max(area, pixels, dynamic range, speed)

- APS will (is) dominating consumer market

- APS can be a single chip solution

- CCD needs clock drivers, digitizers, digital logic so APS is ultimately cheaper for mass-market applications

- One could combine CCD and CMOS, but (so far) there's no commercial push.

- One area where CCDs offer an advantage is:

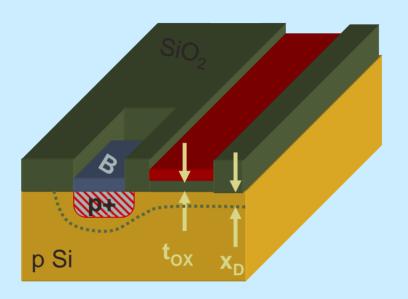

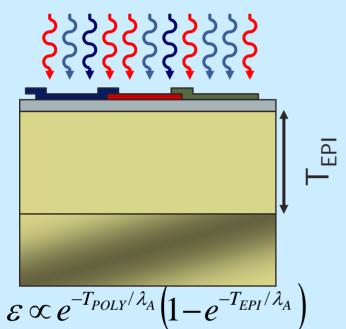

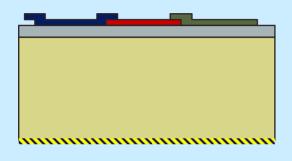

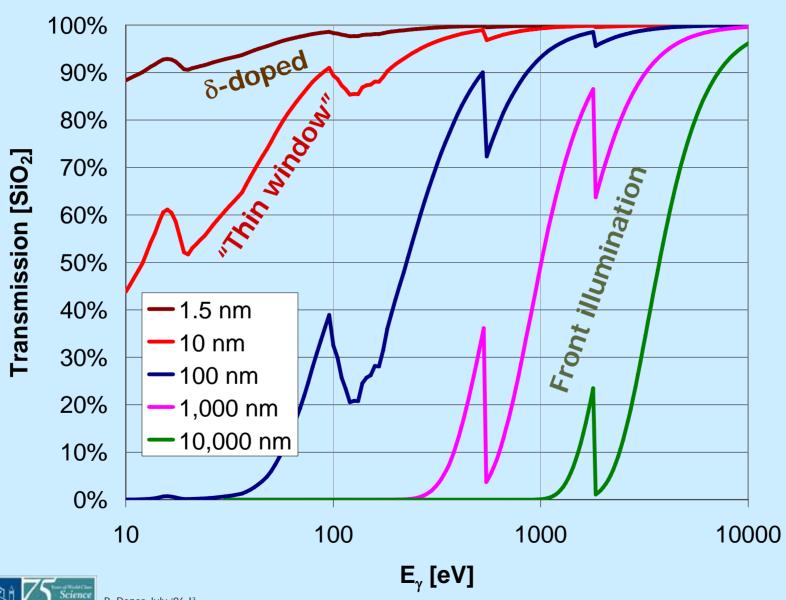

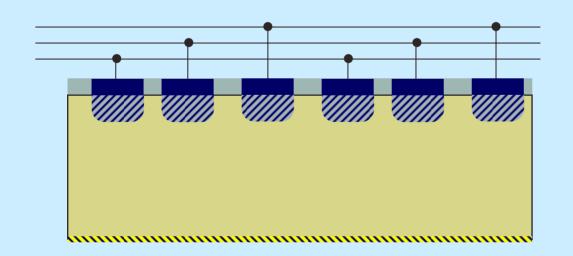

#### Frontside/Backside Illumination

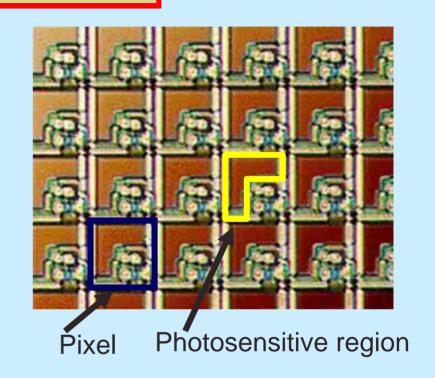

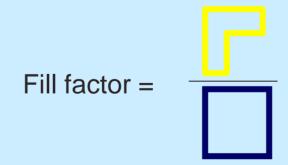

Fill factor < 1

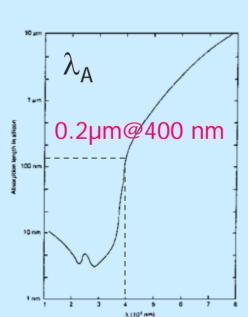

$$\varepsilon \propto \left(1 - e^{-T_{EPI}/\lambda_A}\right)$$

Fill factor = 1

#### **Backside Illumination**

P. Denes July '06 I3

This should be depleted – generally thin with conventional processes

→ add a layer which can be used as an electrode

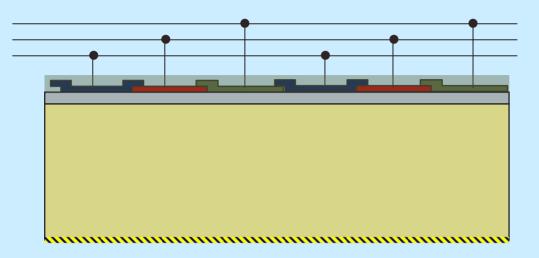

#### PROPOSAL: Make a thick CCD on a high-resistivity n-type substrate, operate fully depleted with rear illumination. 3-phase CCD structure Poly gate Advantages: electrodes 1) Conventional MOS processes with no thinning => "inexpensive" buried p channel 2) Full quantum efficiency to $> 1 \mu m => no fringing$ n--3) Good blue response with $(10 \text{ k}\Omega\text{-cm})$ suitably designed rear contact photo-4) No field-free regions for sensitive charge diffusion, good PSF volume (300 µm) Disadvantages: 1) Enhanced sensitivity to radiation (x-rays, cosmic rays, radioactive decay) Transparent rear window 2) More volume for dark current generation 3) Dislocation generation

LBL CCD - S. Holland et al.

#### **CCDs are wonderful**

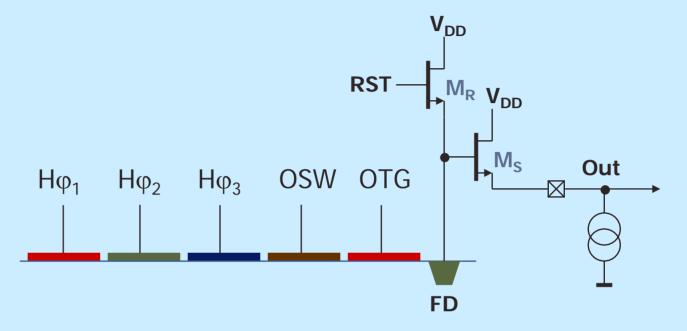

#### But they are slow

- Parallel exposure

- Serial readout

- Vertical clock

- Horizontal clock

- External, high resolution ADC

# Now it gets more difficult

#### Increase ADC speed

top+bottom readout

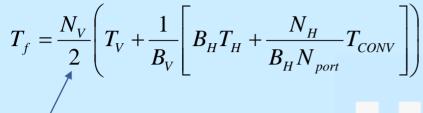

$N_V$ ,  $N_H$  = # H, V pixels  $B_V$ ,  $B_H$  = H, V binning  $T_V$ ,  $T_H$  = H, V shift time  $N_{port}$  = # ports  $T_{CONV}$  = total conversion

time including reset, summing well, ...

#### Limitations

- $\sqrt{kTC}$  Noise contribution from M<sub>R</sub> (reset switch) removed by CDS (correlated double sampling measure V<sub>R</sub> and V<sub>R</sub> + V<sub>S</sub>)

- ♦ Noise contributions from  $M_S$  (source follower)  $\uparrow$  ~  $\sqrt{rate}$

- Ultimately limitations in charge transfer

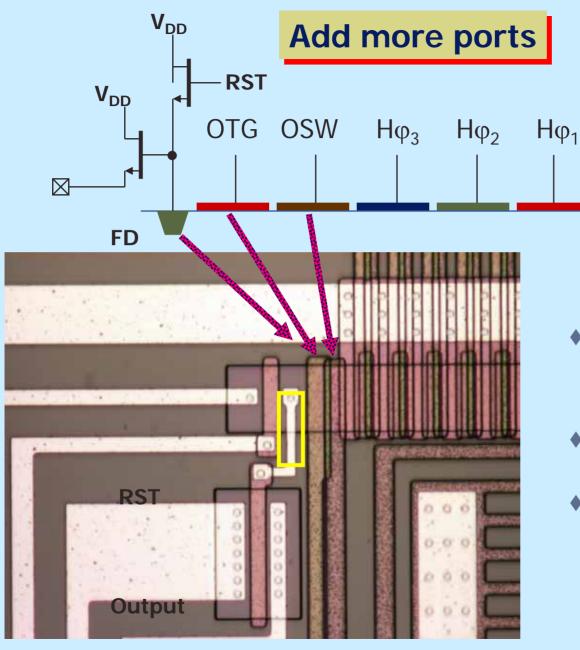

- Reset and output transistors need room

- ♦ Want to minimize C<sub>FD</sub>

- Need space for the output stage!

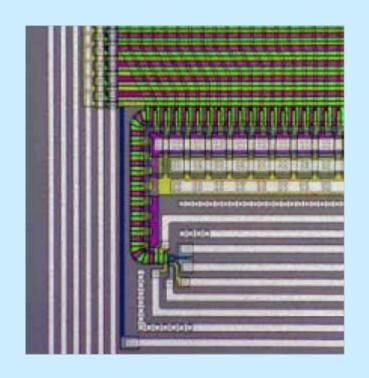

# One way to gain space

Figure 4 Deniction of the region around the output circuit

MIT Lincoln Labs multi-port CCD

#### For example

- Fairchild 456

- 512 x 512 x 8.7 µm pixel (19% FF)

- Interline transfer / 32 ports

- ♦ 1000 fps = 250 MPix/s

- On-chip current sources for 3-stage output ⇒ 2.5 Watts

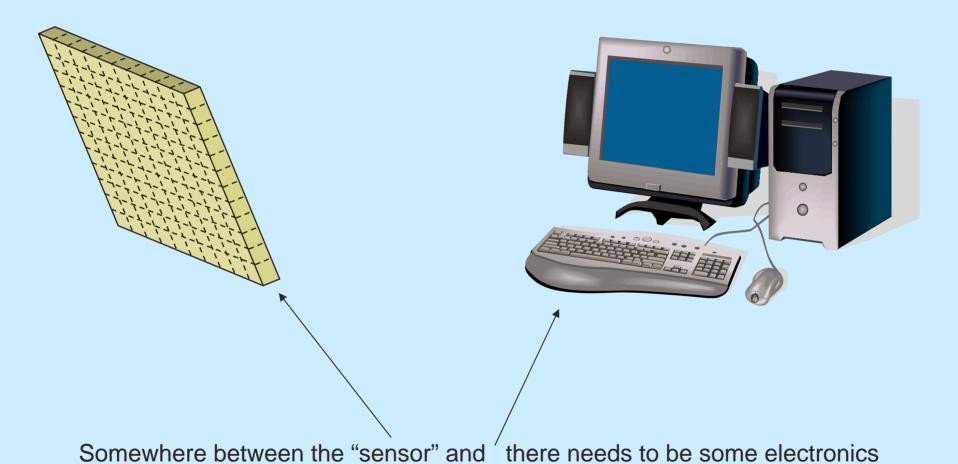

At some point, adding more ADC ports becomes a connection nightmare → integrated circuit solution needed.

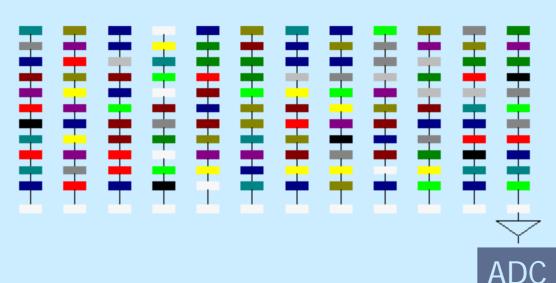

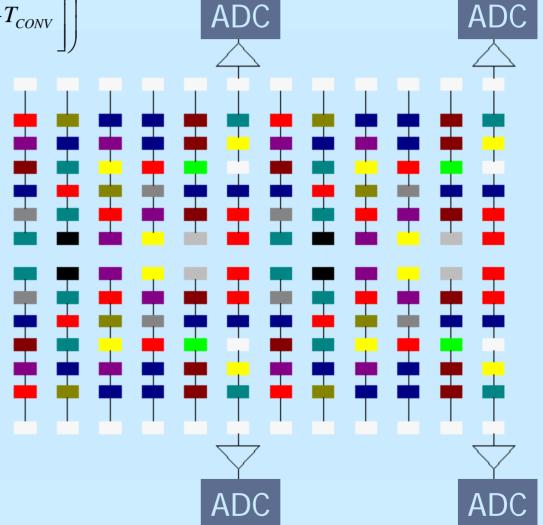

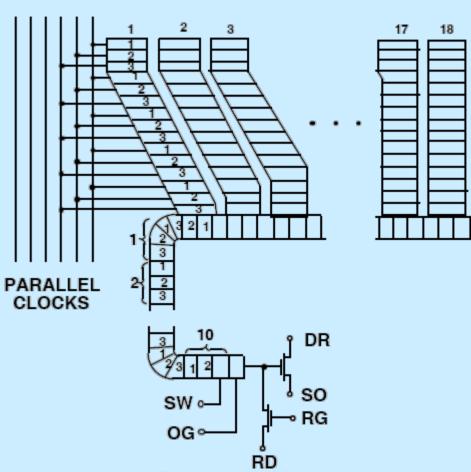

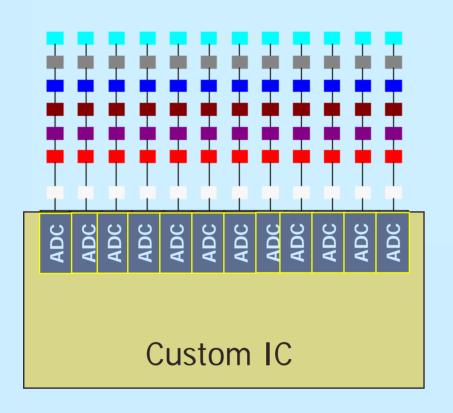

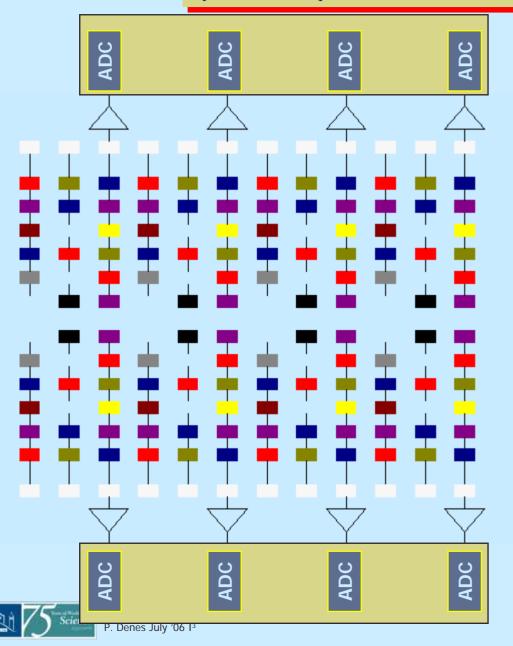

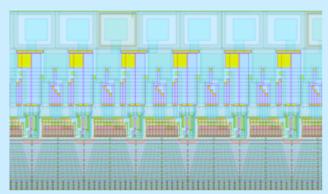

#### Fully column-parallel

- ↑ 1 ADC/column

- Bump bonding required

- No source-follower

- Example developments for ILC Vertex Detector

- 50 MHz column readout

- 4-5 bits dynamic range

RAL et al.

#### (Almost) Column Parallel CCDs

#### **Problem**

CCDs are the ubiquitous imagers for synchrotron radiation applications, but in many cases  $T_{INT} < < T_{RO}$

#### Solution chosen

- Speed increased by N<sub>PORTS</sub>

- N<sub>H</sub> large enough to minimize the number of ADCs needed

- N<sub>H</sub> small enough to ensure fast readout

- Wire bonding still possible

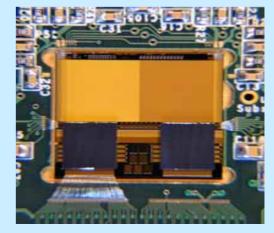

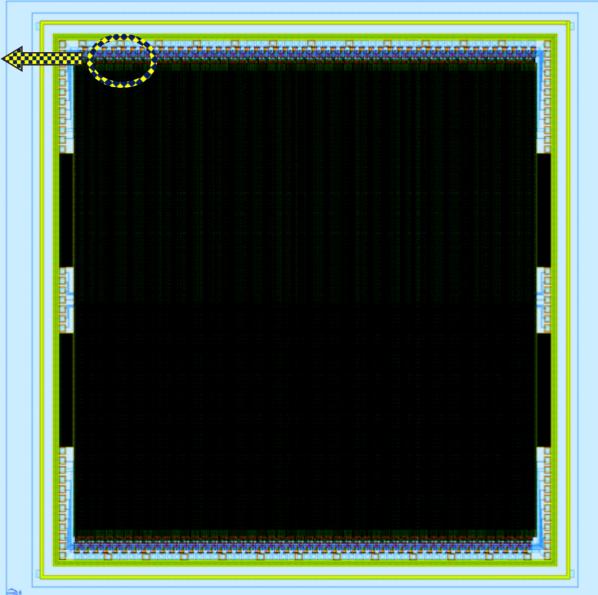

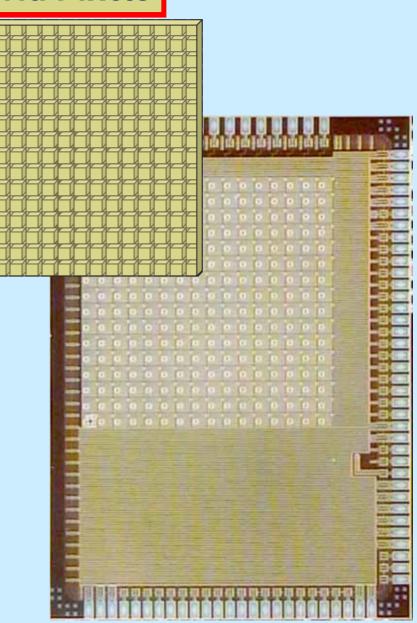

### Prototype – 480 x 480 x 30 µm pixels

- Constant area taper

- 10 pixels/SR

- 300 µm output pitch

- Metal strapped

- ♦ Thick "LBL CCD"

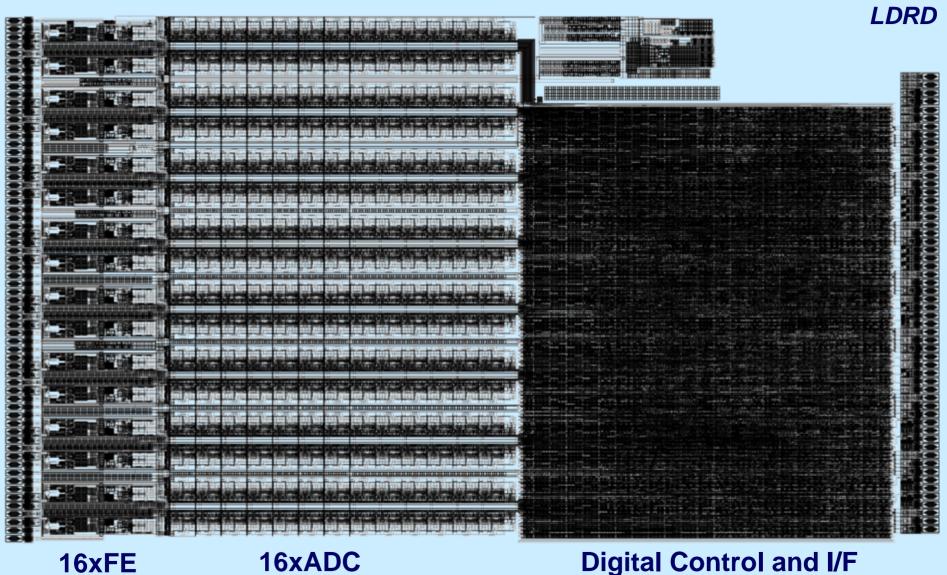

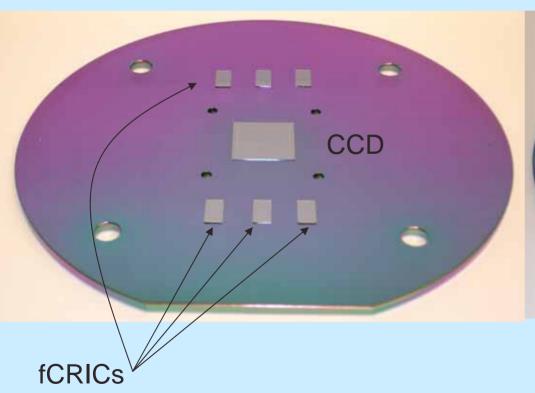

# fCRIC – CMOS 0.25 μm

16xADC

**Digital Control and I/F**

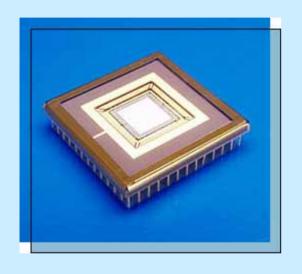

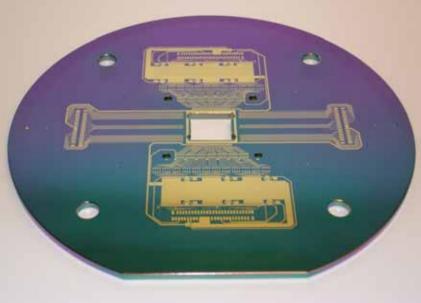

### All Mounted on a 6" Si Substrate

#### "Silicon is a good CTE match to silicon"

### **Fast CCD Camera Specifications**

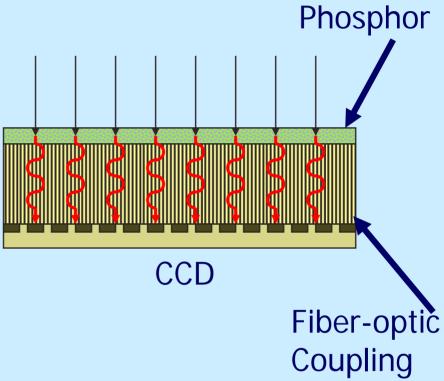

Detection GdO<sub>2</sub>S:Tb phosphor – or – direct

CCD Well depth  $>10^6 e^- (30 \mu m pixel)$

Nominal rate 400 fps (480 x 480, "zero integration")

Sensitivity at nominal rate 3.5 µV/e<sup>-</sup>

FS at nominal rate 128k e<sup>-</sup>

Noise at nominal rate <10 e<sup>-</sup>

Conversion gain fixed by CCD and integration time. Larger FS possible with shorter integration time.

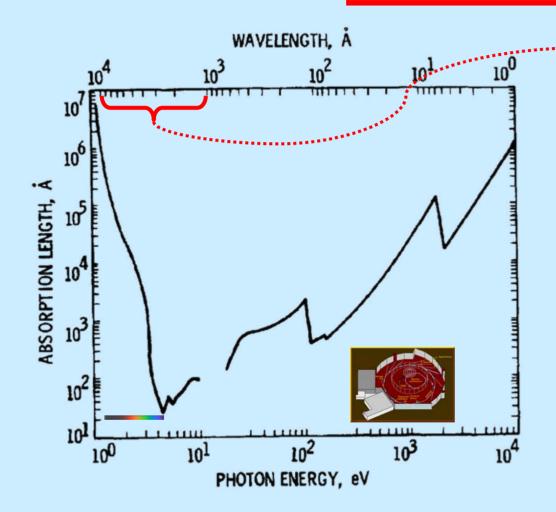

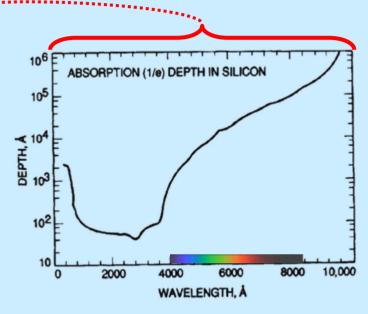

#### **Absorption in Si**

Ignoring reflection ...

Visible light or x-rays: 4-5 orders of magnitude

Bandgap of Si at 300K = 1.1 eV  $\rightarrow$  pure Si transparent for  $\lambda$  > 1.1  $\mu$ m

From Janesick

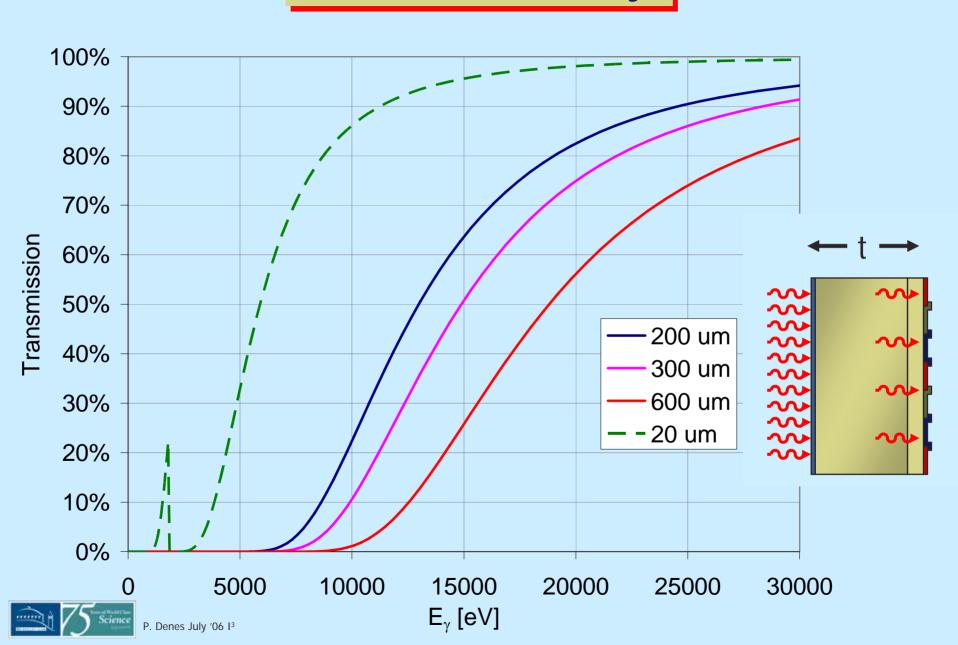

# Thick Silicon for x-rays

# **Back-illumination preferred**

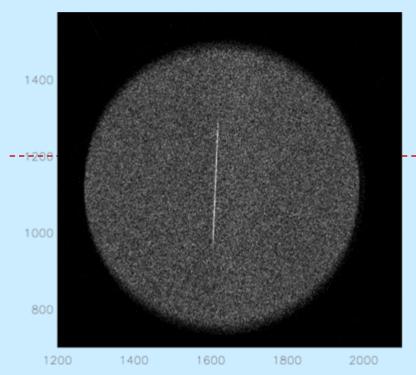

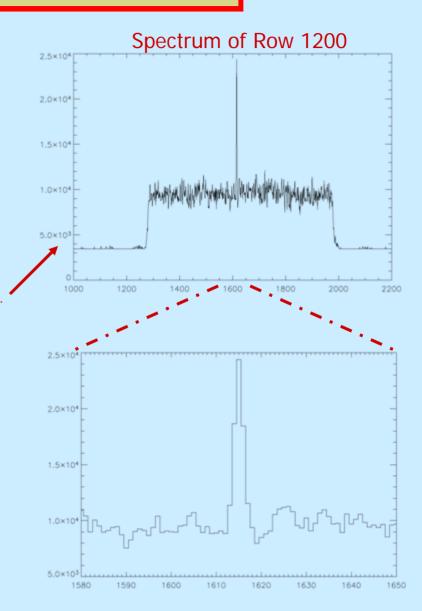

# 1st x-ray images in LBNL CCD

3,512 x 3,512 x 10.5µm pixel CCD 200 µm thick Cu anode, 140K, 70 kHz

5 μm slit in semi-transparent stainless steel

# x-rays in CCDs

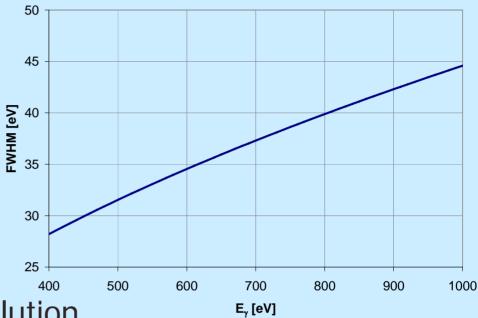

#### Intrinsic resolution in Si

- Excellent spectroscopic resolution

- But only if not piled-up low rate or fast readout

- $N_{\gamma,MAX}$  = Well Depth /  $(E_{\gamma}/3.6 \text{ eV})$

- < 1000

- $\Rightarrow$  9-10 bit ADC OK

- Would really profit from high-speed readout as S/N is so high

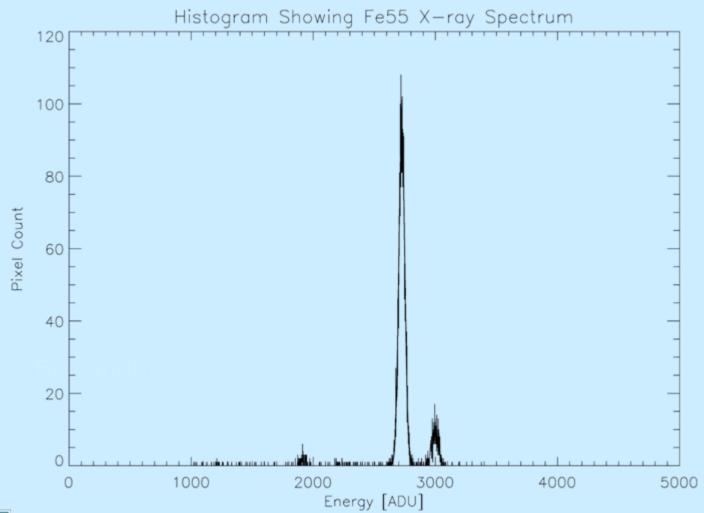

# 650 µm thick CCD

# <sup>55</sup>Fe $K_{\alpha}$ and $K_{\beta}$ . Resolution ~ 126 eV at 5.6 keV

# pn-CCD

LBL CCD

pn-CCD (MPI, ...) (Gatti, Rehak, Struder ...)

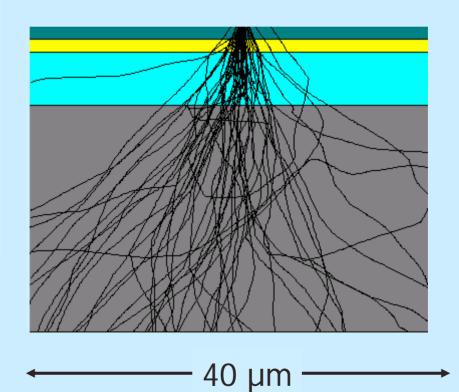

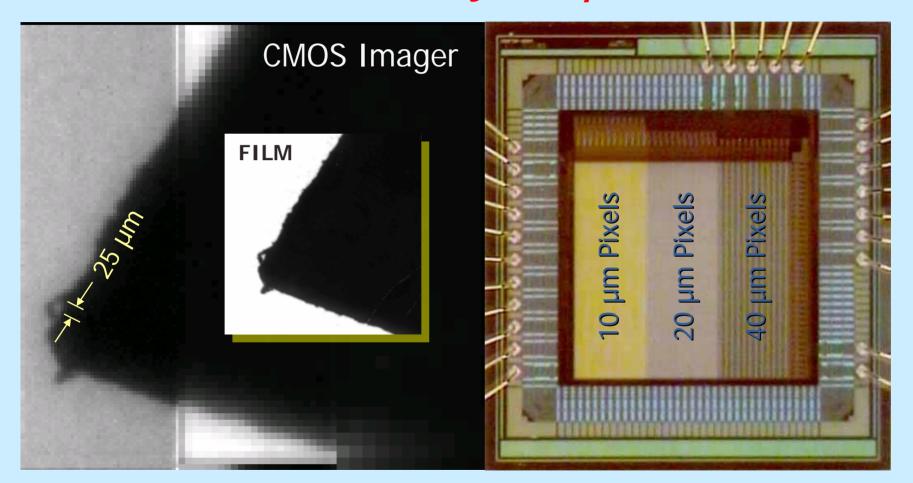

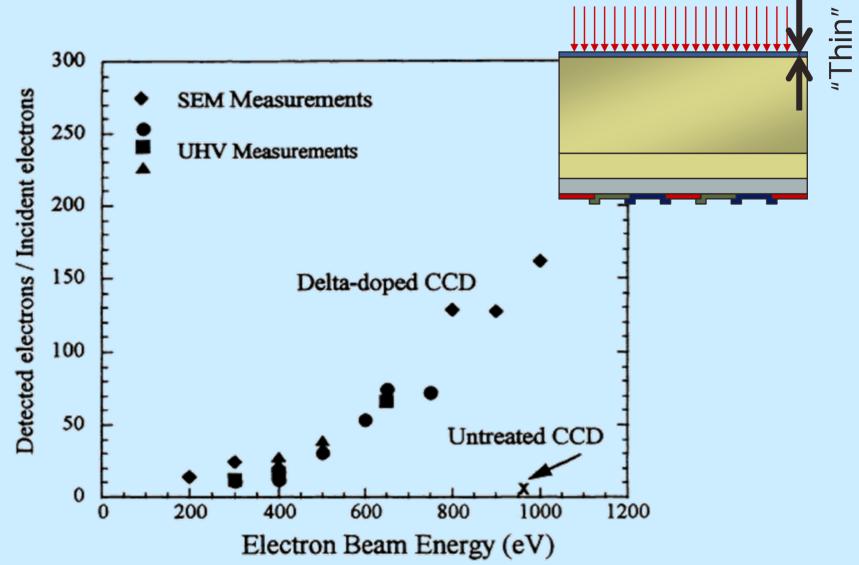

# **Electrons**

#### **EM Detector**

#### The Problem:

300 keV, 1 mm

$R [\mu m] \sim E [keV]$

#### **The Solution:**

300 keV e-

4 μm SiO<sub>2</sub> 2 μm Al 2 μm SiO<sub>2</sub> 8 μm active Si

**Inactive Si**

50 µm total

### **Optical** Active Pixel

Fill Factor = Active / Total area

# **EM Active Pixel**

Fill Factor = 100%

# Radial Distribution [300 keV]

### Image of Beam Stop (200 keV)

#### PSF visibly < 10 μm

Noise limited - no cooling

**Test Chip in AMS C350**

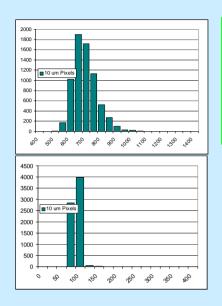

#### Monolithic Imagers for EM

Signal: 25 mV/e<sup>-</sup> (200 keV)

Noise 3.0 mV

- Single electron sensitivity (SNR 8.3 here, will improve with cooling)

- ~μm PSF

- High-speed readout (dynamics)

Next step: 3k x 3k high-sensitivity (bio) chip

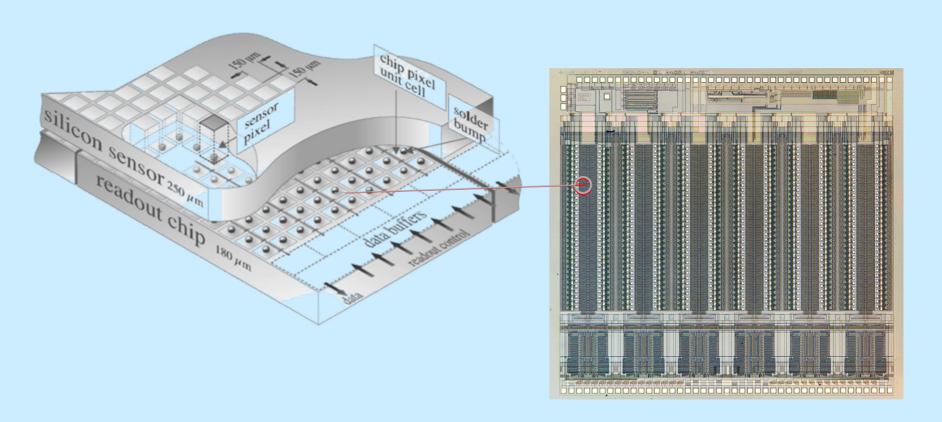

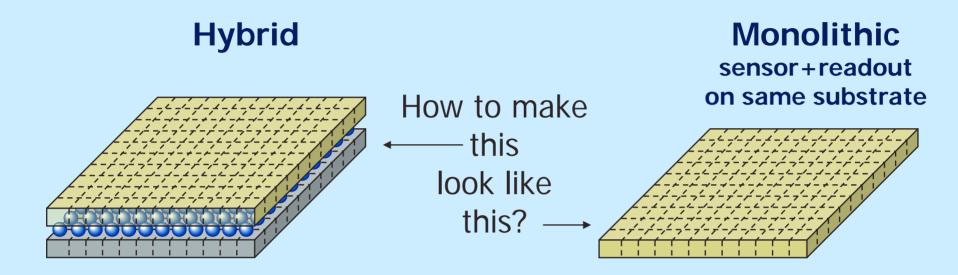

#### **Hybrid Pixel Detectors**

Advantage over monolithic detectors: much more sophisticated electronics per pixel

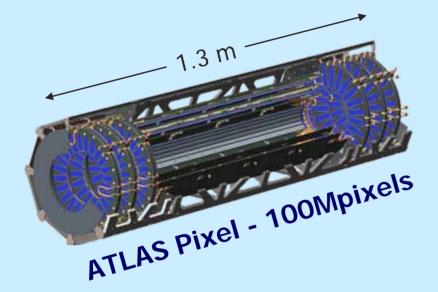

### e.g. ATLAS Pixel Detector

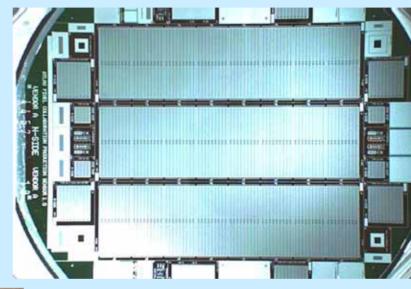

100 mm wafer with 3 Si sensors

Readout ICs

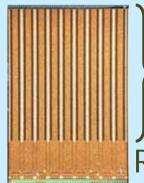

18x160 pixels

Readout

A "module" is 1 sensor with 2x8 bump-bonded chips

# **②** and **⊗** of Hybrid Pixels

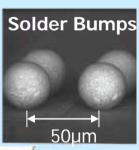

- Interconnect generally implies relatively large pixels

- Large pixels can have much more "intelligence"

- measure per event (e.g. E, t)

- complex functions (e.g. temporal autocorrelation)

- spectroscopy

- Large pixels make large pixelcount detectors challenging (c.f. ATLAS pixel detector)

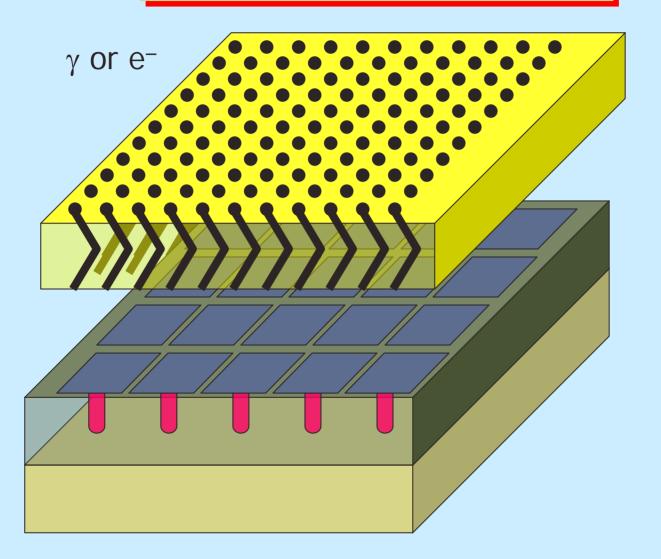

# **Another kind of Hybrid Pixel**

**MCP**

Readout chip or CCD (esp. LBL CCD)

MCP – large electron multiplication gain

# For e- Maybe LBL CCD and no MCP

# Monolithic Hybrid Detectors?

Bump-bonding works, but is "R&D" for pitch  $< \sim 200 \ \mu m$  and is best done "wafer scale"

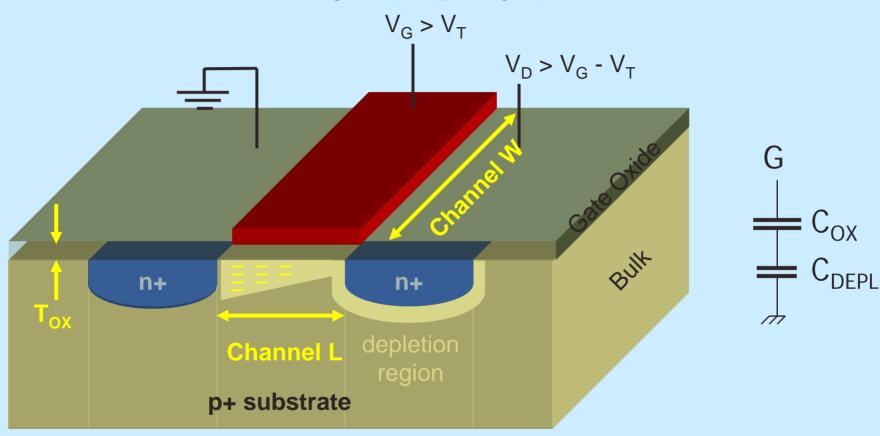

# (Bulk) MOS Transistor

Saturation –

$$V_G > V_T$$

,  $V_D > V_G-V_T$

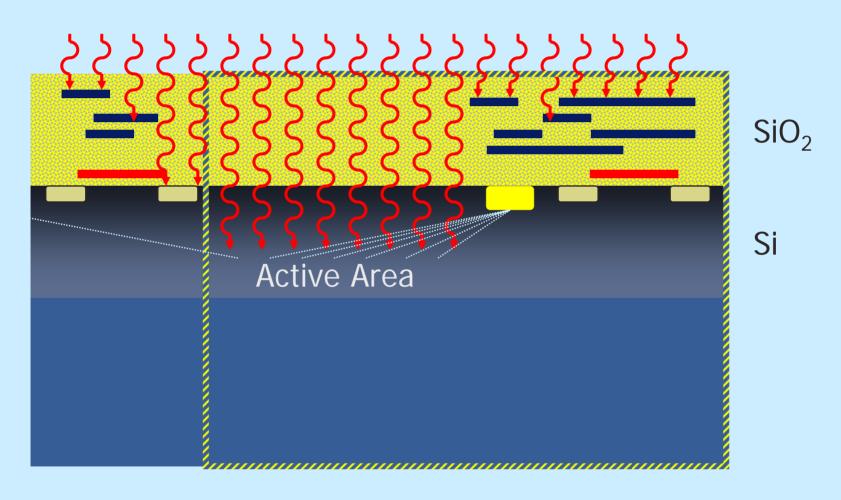

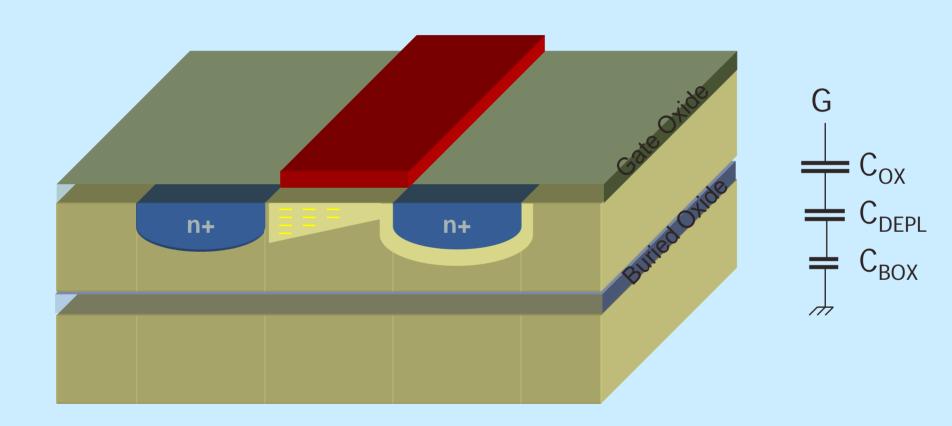

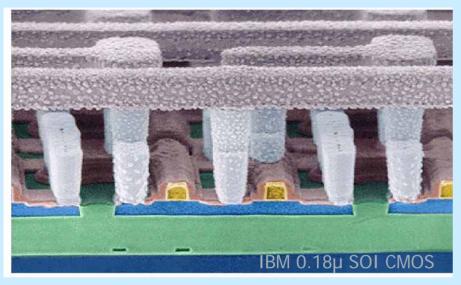

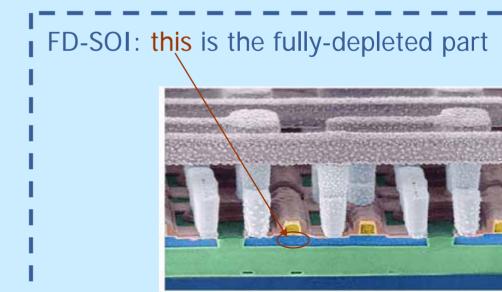

# Silicon-On-Insulator

### **Advantages of SOI**

Metal Interconnect

Metal Interconnect

Polysilicon gate

Box

- Reduces substrate coupling

- higher speeds

For lowest power, want a high-resistivity substrate

- lower power

- Improves radiation hardness

- no latch-up through substrate

- complete di-electric isolation possible (with trench isolation)

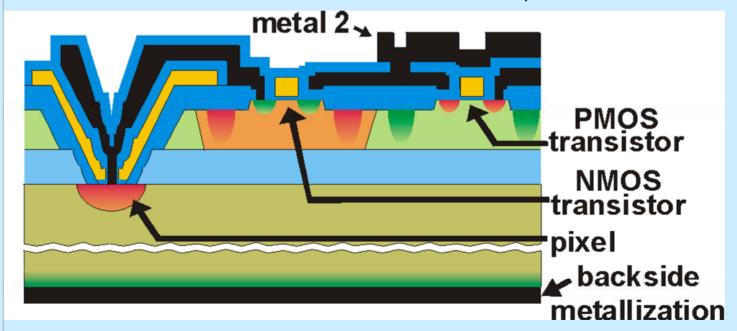

### "Artisanal" SOI Pixel

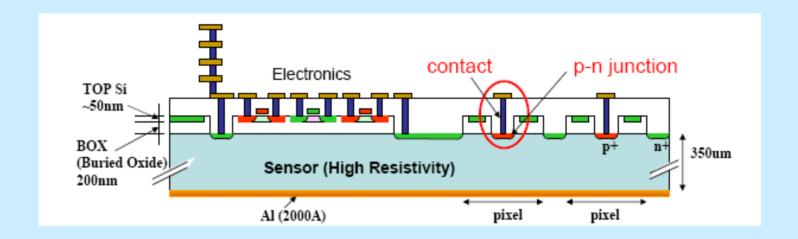

### SOI Imager - Main Concept

### **Detector** → handle wafer

- High resistive

- 300 µm thick

### **Electronics** → device layer

- Low resistive

- ■1.5 µm thick

J.Marczewski

European project SUCIMA

3

### Saved by the Watch?

- Commercial SOI on highresistivity silicon (without contact)

- 0.15 μm CMOS

- Dream process?

- Almost see next page

- KEK HEP group working on SOI pixels for particle tracking

#### Fully-depleted Type SOI Device Enabling an Ultra Low-power Solar Radio Wristwatch

Masafumi Nagaya

On May 19, 2002, Casio Computer Co., Ltd. Isunched sales of the Tool Concept PRIS-50, a new addition to its Pro Trek series of "outdoor" watches which provide compass direction and altitude readings. Moreover, these watches run on solar power, so there is no need to worry about battery replacement. (See Fig. 1.)

The Tool Concept PRG-50 employs a low-power LSI IC designed for watches which induces an Oki Electric fully-deplated type SQI (Silicon-On-Insulator) CMOS device (PDSCI-CMOS) <sup>1) 27</sup> for greatly-reduced current consumption. Thanks to the high-fertormance coler drive system built into this chip, plus a solar panel that provides highly efficient power generation and a high-storage-capterly battery, this watch is able to use solar power to operate direction and attitude functions-features not found in conventional solar watches. As such, the Tool Concept PRG-50 is a high-performance outdoor watch that hiteas and trakters can trust, without any worties about low batteries.

The following <sup>5</sup> describes how the fully-depleted type SOI CMOS device (FDSOI-CMOS) was developed for Casio for use as a waith-type LSI IC (product name: MLE(26) that boasts the world's lowest current consumption.

Fig. 1 Tool Concept PNG-50

#### Reducing Current Consumption In LSI ICs for Watches

The push for lower current consumption in Casions. LSI ICs for watches began in earnest around 1927. In addition to meeting the niseds for longer watch battery life and reduced environmental impact, Casio was seeking to use thinner button-type batteries to power that watcher Using these button batteries would enable the watch itself to be made thinner and more fashionable

Conventional IC chips for watches, such as the MSMS118, were rated (in chip-specific electrical characteristics) to consume 1.55 µA of current. Since 1997, current consumption has been successively reduced by circuit design measures, use of the multiple fineshold value process, and layout techniques scaled to 1.3 µA (in the MBMS121), then to 9.7 µA (in the MBMS121), then to 9.7 µA (in the MBMS121), then to 9.7 µA (in the require only the lower threshold value process uses at least two different threshold value one designed to use that lower value while other translators but the higher threshold value, which enables both low leakage outrent and low-votage operation.)

in the MSM6122, when the threshold value is at the center of the target value range, the chip's actual current consumption is raised to 0.35 µA, and when the threshold value is at the worst level, the leakage current is increased such that the current rating becomes 0.7 µA. At the same time, even when the threshold value is at the center of the target value range, the charge-discharge current for the crystal oscillator circuit, main clock circuit, and display discuits made it difficult to reduce current consumption. Consequently an FOSIC-CMOS process using tilly-depleted type SOI was adopted as a solution for reducing current consumption.

#### Advantages of the FDSOLCMOS Process

Listed below are some of the advantages of using the FDSOLCMOS process as a means of reducing current consumption in LSI ICs for walthes.

- Low parasitic capacitance

- The fineshold voltage can be set lower than in bulk devices.

These advantages are further described below.

The junction capacitance that is a component of a MOS trahsister's parasitic capacitance is proportional to be junction surface area, and the junction surface area is the sum of the plane and lateral surface area is the sum of the plane and lateral surface area of the sourcelation diffusion layer. In POSI-CIMOS devices, the bottom surface is connected to a thick code film (enthedded code film), which greatly reduces appealance 9. As for the lateral areas, only the parts that tace channels are affected, and the overall capacitance is reduced to about one tenth that of the sourcelatinal junction area in conventional bulk devices. Accordingly, the capacitance subject to load charges and discharges is reduced, making for lower current for the watch's LCO driver block, flaculp, and size-deban circuits can be

### Modified Version of Oki 0.15 µm FD-SOI

- 3 extra masks needed: (p+ and n+ implants and contact)

- Metal back-side contact

- "quasi commercial"

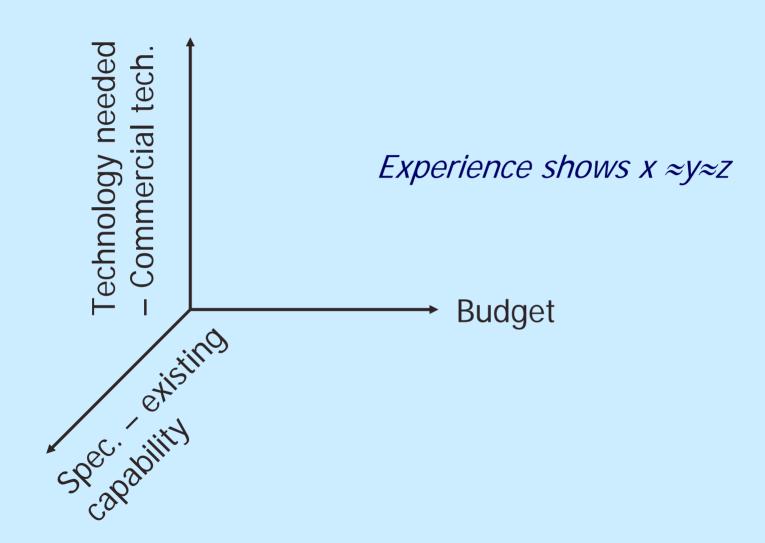

### Caveat emptor

### Many Interesting Challenges – to be solved

Microsystems Lab

Systems Expertise

Unique IC skills

- + materials development (life after Si?)

- + ...

- + (most important) user base

Then: "You push the button, we do the rest"

Now: "We do the rest, you push the button"